印刷电路板(PCB板)制造商在提高可靠性和降低成本的同时,也面临着增加密度、缩小占位面积、减少侧面尺寸、管理热流和提高数据速率等重大压力。随着他们不断成功地消减这些压力,一个有趣的挑战出现在设计师们的面前,即在两片PCB板之间去对齐多个已配对连接器组。

我们所需要的是清晰明确的准则,以在不牺牲系统性能、密度和可靠性的情况下,懂得如何应对这些对齐挑战,同时满足日益严格的预算和上市时间要求。

本文在描述先进的PCB和更可靠的高密度连接器之间可能遇到的冲突性要求之前,将更详细地讨论对齐的挑战,从而可以通过使用设计最佳实践高效地满足这些要求。

小型化使连接器对齐变得困难

PCB板有许多可以改进的方向,包括密度、更高的数据速率、热管理和可靠性。然而,伴随着这些改进的是小型化这一趋势在连接器的选择和实现方面为设计师带来的压力,特别是将多个连接器配对到PCB板上。

就连接器而言,在过去25年中,小型化导致间距从0.100英寸(2.54毫米)下降到0.016英寸(0.40毫米)——也就是减小了六倍,因此需要更严格的公差。然而,更严格的公差本身并不是问题,问题在于标称公差周围的可变性:如果多个连接器变至标称的任一极限,则更有可能出现一些问题。

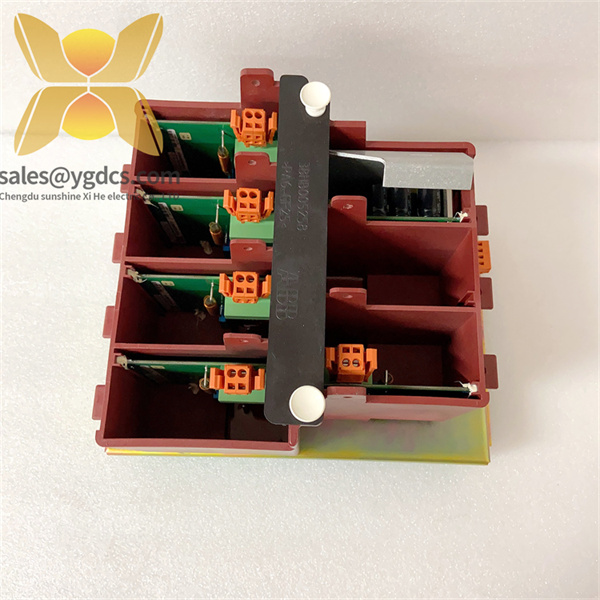

采用单个配对连接器组的应用不会出现问题:因为没有公差累加,夹层卡被假定是自由浮动的,并且连接器的整体和局部对齐功能将确保完美对齐(图1,顶部)。